三維集成電路TSV布局設計 架構、挑戰與優化策略

引言

隨著摩爾定律的演進逐漸逼近物理極限,三維集成電路(3D IC)技術通過垂直堆疊多個芯片層,并利用硅通孔(Through-Silicon Via, TSV)進行層間互連,成為延續集成電路性能提升、實現高密度集成與異構集成的重要途徑。TSV作為3D IC的“垂直高速公路”,其布局設計直接關系到系統的性能、功耗、可靠性和制造成本,是三維集成電路設計中的核心環節。

TSV布局設計的關鍵考量因素

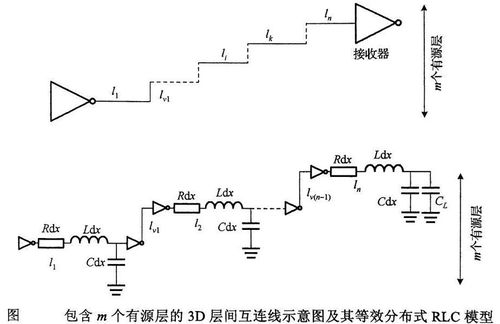

- 電氣性能:TSV本身具有寄生電容、電阻和電感,其布局會影響信號完整性、延遲和功耗。設計時需考慮TSV的尺寸、間距、深度以及與晶體管、互連線的相對位置,以最小化寄生效應,確保高速信號傳輸質量。

- 熱管理:三維堆疊加劇了熱積累問題,TSV作為金屬填充結構,具有較高的熱導率,可作為有效的散熱路徑。優化TSV布局,如在熱點區域密集排布TSV,能顯著改善芯片的散熱能力,防止局部過熱導致的性能下降或可靠性問題。

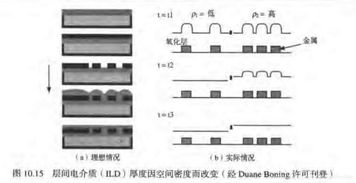

- 機械應力與可靠性:TSV與硅襯底之間存在熱膨脹系數失配,在制造和工作中會產生機械應力,可能導致晶格缺陷、載流子遷移率變化甚至TSV開裂。布局設計需通過仿真分析應力分布,避免在敏感電路(如存儲單元、模擬電路)附近放置過多TSV,或采用應力緩沖結構。

- 面積開銷與制造成本:TSV占用寶貴的芯片面積,其制造工藝復雜、良率挑戰大。設計需在滿足互連需求的前提下,盡可能減少TSV數量、優化其占位,并考慮與后端布線(BEOL)的協同,以降低整體成本。

- 設計與工藝協同:TSV布局必須與芯片的制造工藝節點、鍵合技術(如面對面、面對背)、TSV形成順序(先通孔或后通孔)等緊密結合。不同的工藝選擇會對TSV的密度、深寬比、電學特性提出不同的約束。

TSV布局的主要策略與方法

- 規則陣列布局:將TSV在芯片平面內按規則網格(如矩陣)均勻分布。這種方法設計簡單,易于與全局時鐘網絡、電源地網絡集成,有利于均勻散熱和降低布線擁塞。但可能不夠靈活,無法針對特定模塊的互連需求進行優化,導致TSV利用效率不高。

- 模塊感知的定制化布局:根據芯片各功能模塊(如處理器核、緩存、I/O)之間的通信帶寬和延遲要求,將TSV集群放置在需要高帶寬垂直互連的模塊上方或附近。這種方法能最大化互連效率,減少全局互連長度,但布局復雜,需要先進的電子設計自動化(EDA)工具支持。

- 電源/地TSV與信號TSV協同布局:電源傳輸網絡(PDN)在3D IC中面臨更大挑戰。通常將電源/地TSV與信號TSV分開規劃或交織布局,以確保穩定的供電和低噪聲。例如,采用電源TSV“圍欄”為信號TSV提供回流路徑,減少信號串擾。

- 熱驅動布局優化:利用熱仿真工具,識別芯片的熱“熱點”,并主動在這些區域插入或密集排布TSV,將其作為“熱通孔”將熱量傳導至散熱蓋或下層。需避免因TSV布局不當造成新的熱瓶頸。

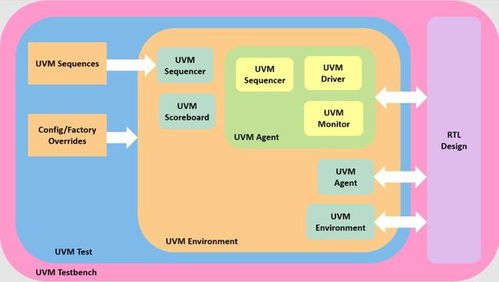

- 基于EDA工具的自動化與協同優化:現代3D IC設計嚴重依賴EDA工具鏈。高級綜合(HLS)、布局布線(P&R)工具需要集成TSV模型,支持在系統級、架構級就考慮TSV的影響,實現TSV數量、位置、布線、時序、熱、應力的多目標協同優化。

挑戰與未來展望

盡管TSV布局設計技術已取得長足進步,但仍面臨諸多挑戰:

- 多物理場耦合分析的復雜性:電-熱-機械效應的強耦合使得精確仿真和優化極其復雜。

- 異構集成帶來的新問題:將邏輯、存儲、射頻、傳感器等不同工藝、不同功能的芯片進行3D集成時,TSV布局需要滿足更復雜的異構互連與隔離需求。

- 測試與可制造性設計(DFM):如何為包含大量TSV的3D IC設計高效的測試架構,并在布局階段就考慮工藝變異、缺陷對良率的影響,是量產的關鍵。

隨著芯粒(Chiplet)和先進封裝技術的發展,TSV可能會與微凸塊、再布線層(RDL)等互連技術更緊密地融合。TSV布局設計將進一步提升至系統-封裝協同設計(Co-Design)的層面,從整個電子系統的角度尋求最優的垂直互連解決方案,從而持續釋放三維集成的巨大潛力。

###

三維集成電路中的TSV布局設計是一個多維度的優化問題,需要在性能、功耗、熱、可靠性和成本之間取得精妙平衡。它不再是傳統二維設計后的簡單附加步驟,而是需要貫穿于3D IC設計早期架構規劃直至物理實現的全過程。深入理解TSV的物理特性,掌握先進的布局策略與EDA工具,是成功設計高性能、高可靠三維集成電路的基石。

如若轉載,請注明出處:http://www.9c4gcj.cn/product/60.html

更新時間:2026-01-07 06:38:25